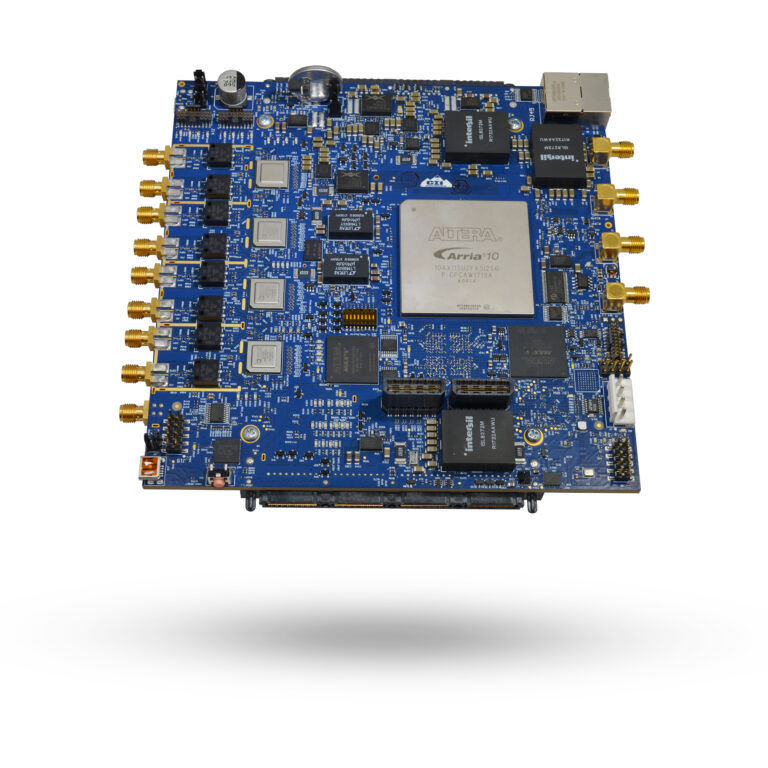

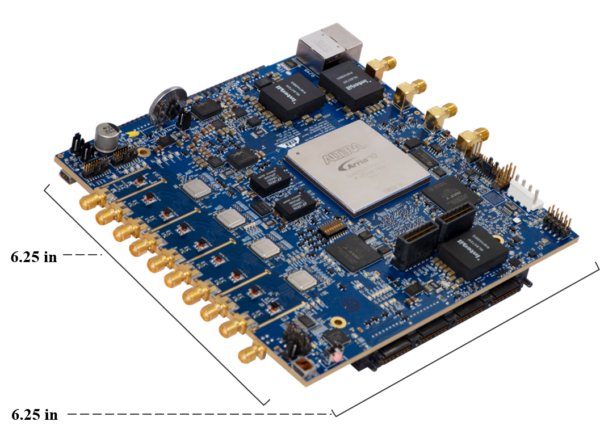

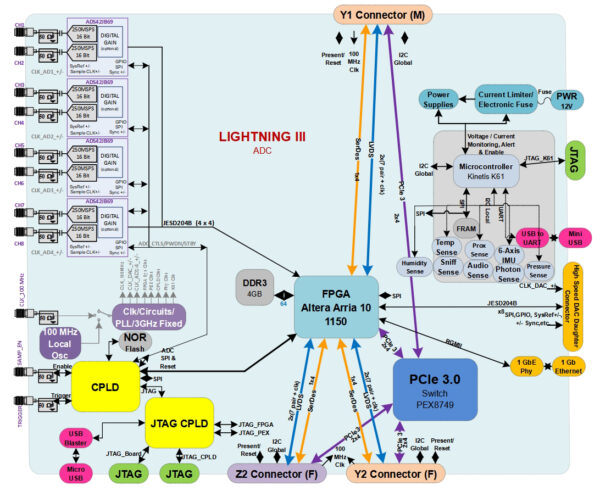

3DR Lightning III – 8-Channel, 16-Bit, 250 MSPS Analog-to-Digital Converter

The 3DR-A10-ADC-250MSPS, known as Lightning III, is an 8-channel, 16-bit, 250 MSPS analog-to-digital converter board for digitizing and processing analog inputs. High performance, low latency processing can be implemented via the on-board Altera Arria 10 FPGA (10AX115U2F45I2SG).

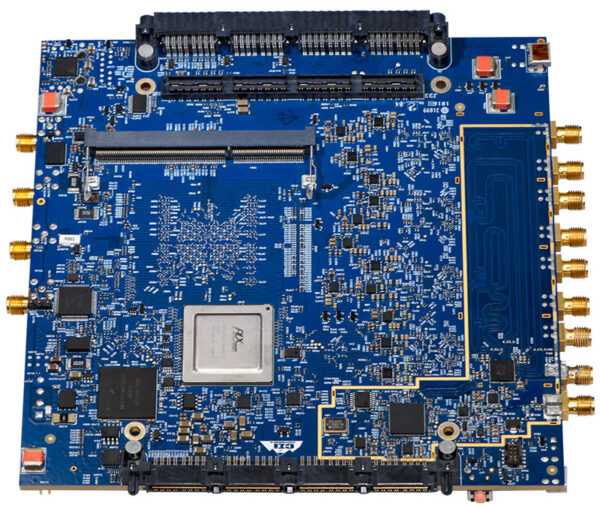

As with all 3DR computing modules, Lightning III supports three-dimensional connectivity, allowing the user to stack and/or tile modules to address a wide variety of processing, I/O, size, weight, and power requirements. Lightning III provides PCIe and LVDS interfaces via the Y and Z connectors to other modules in the 3DR computing family. It also offers additional external interfaces including SMA connections for clocking and triggering flexibility.

- Digital signal processing/data acquisition

- Radar receiver (digital receiver)

- Digital array processing and beamforming

- Electronic warfare/attack systems

Features

FPGA

- Altera Arria 10: 10AX115U2F45I2SG

- 4 GB DDR

Analog – ADS42JB69

- Dual-channel 16–bit ADC

- 250 Mega–Samples Per Second (MSPS)

- Data rates up to 3.125 Gbps

- JESD204B serial interface with up to

four lane support - SNR: 73.3 dBFS, SFDR 93dBC @

170MHz, 2Vpp, –1dBFS

External I/O Support Available Via:

- Y-connector (2x)

- Z-connector (1x)

- JTAG

- 4x—40 GbE daughter card

- SMA

- UART

Tailored Clocking and Triggering Flexibility

- Sample gates (SMA) in/out

- Trigger (SMA) in/out

- Clock inputs (SMA)

- On-board clock

Standard 3D Computing

- K61 microcontroller interface

- Controls power-on and power-down sequencing

- Monitors voltages and report faults over I2C bus

- Monitors current, e-fuse shut-down, and reports over I2C bus

- Monitors board temperature over I2C bus (external sensor available)

- On board EEPROM for data storage and logging (write protect available)

- FPGAs and CPLDs programmable over JTAG bus (for applicable modules with FPGAs and CPLDs), or via connectors from other 3DR computing boards (firmware required)