3DR Lightning I – 4-channel, 12-bit, 10 GSPS Analog-to-Digital Converter

Home>Boards and Modules>Computing>Embedded>3DR Lightning I – 4-channel, 12-bit, 10 GSPS Analog-to-Digital Converter

Description

Applications

Downloads

Request a Quote

Description

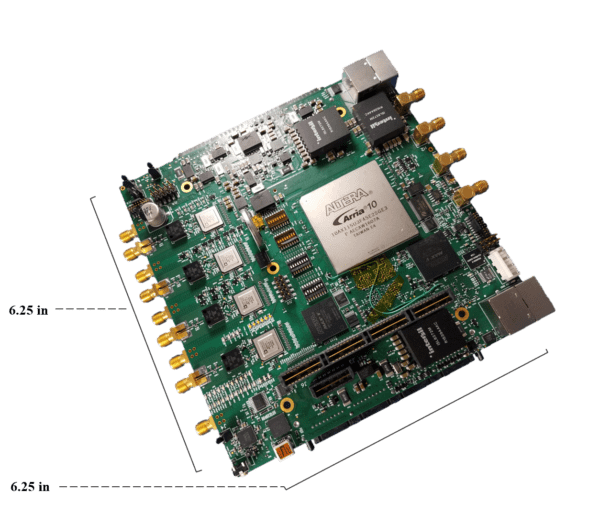

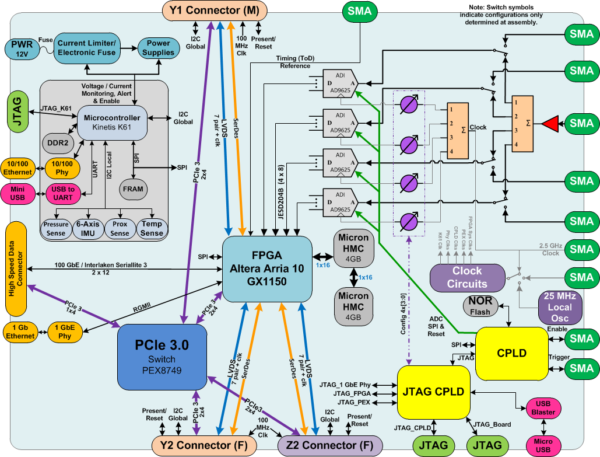

The 3DR-FPGA-ADC-10GSPS is a 4-channel, 12-bit, 10 GSPS analog-to-digital converter board for digitizing and processing analog inputs. High performance, low latency processing can be implemented via the on-board Altera Arria 10 FPGA (10AX115U3F45I2SG). As with all 3DR computing modules, the 3DR-FPGA-ADC-10GSPS supports three-dimensional connectivity, allowing the user to stack and/or tile modules to address a wide variety of processing, I/O, size, weight, and power requirements.

This product has reached end-of-life (EOL) – please contact us about its upcoming replacement.

Applications

- Digital signal processing/data acquisition

- Radar receiver (digital receiver)

- Digital array processing and beamforming

- Electronic warfare/attack systems

Downloads

Request a Quote

Features

FPGA

- FPGA Altera Arria 10

- 10AX115U3F45I2SG

- 2x—Hybrid Memory Cube (HMC)

Analog-to-Digital Conversion

- 4×2.5 GSPS channels non-interleaved

- 2×5 GSPS channels interleaved

- 1×10 GSPS channel interleaved

- 12-bit

- >8 ENOB

- Non-linear equalizer IP

- >4 GHz instantaneous bandwidth

Clocking and Triggering Flexibility

- Sample gates (SMA)

- Trigger (SMA)

- Clock inputs (SMA/TwinAx)

- ToD—Time of Day

I/O Support Available Via:

- Y-connector (2x)

- Z-connector (1x)

- High speed connector (1x Top)

- JTAG

- 4x—40 GbE daughter card