4 Channel, 12-bit, 10GSPS Analog-to-Digital Converter

Model Number: 3DR-A10-ADC-10GSPS

# **3D COMPUTING OVERVIEW**

3DR computing technology brings together high performance computing, ease of programmability, low-cost, and commercial I/O flexibility in a modular, open systems and standards architecture to realize uniquely scalable and widely configurable, high speed embedded processing solutions for the development of radar, EW, SIGINT, and communication systems.

3DR computing possesses the unique ability to morph in size, shape, and processing capacity. This flexibility provides a low cost, standard solution capable of rapidly conforming to the vastly different power, space, and environmental requirements found aboard any surface, sub-surface, or airborne system or platform.

### PRODUCT DESCRIPTION

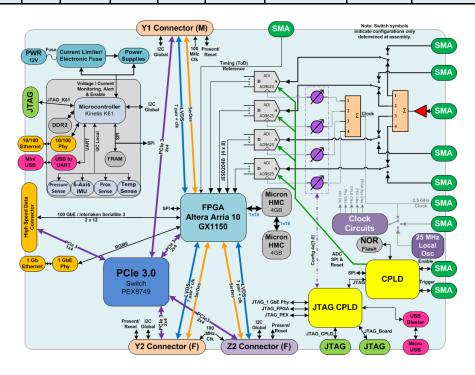

The 3DR-A10-ADC-10GSPS, known as Lightning 1, is a 4 channel, 12-bit, 10GSPS Analog-to-Digital converter board for digitizing and processing analog inputs. High performance, low latency processing can be implemented via the onboard Altera Arria 10 FPGA (10AX115U3F45I2SG).

As with all 3DR computing modules, Lightning 1 supports three dimensional connectivity, allowing the user to stack and/or tile modules to address a wide variety of processing, I/O, size, weight, and power requirements. Lightning 1 provides PCIe and LVDS interfaces via the Y and Z connectors to other modules in the 3DR computing family. It also offers additional external interfaces including Twinax, and SMA connections for clocking and triggering flexibility along with Time of Day (ToD).

# **FEATURES**

#### **FPGA**

- Altera Arria 10

- 10AX115U3F45I2SG

- 2x—Hybrid Memory Cube (HMC)

### **Analog-to-Digital Conversion**

- 4x2.5 GSPS channels non-interleaved

- 2x5 GSPS channels interleaved

- 1x10 GSPS channel interleaved

- 12-bit

- >8 ENOB

- Non-linear equalizer IP

- >4 GHz instantaneous bandwidth

# Clocking and Triggering Flexibility

- Sample gates (SMA)

- Trigger (SMA)

- Clock inputs (SMA/Twinax)

- ToD-Time of Day

### I/O Support available via

- Y-connector (2x)

- Z-connector (1x)

- High speed connector (1x Top)

- JTAG

- 4x—40 GbE daughter card

# APPLICATIONS BENEFITS

- Digital signal processing/ data acquisition

- Radar receiver (digital receiver)

- Digital array processing & Beamforming

- Electronic warfare/attack systems

- Enough FPGA flash memory to hold two FPGA configurations

- On board circuitry fuse and temperature monitoring for board protection

- Standard 4-pin power connector

4 Channel, 2.5 GSPS Non-Interleaved ADC, >8 ENOB 2 Channel, 5 GSPS Interleaved ADC, >8 ENOB \* 1 Channel, 10 GSPS Interleaved ADC, >8 ENOB \* \* Requires interleaving board

SBIR DATA RIGHTS: Contract#: HQ0006-08-C-7908 Contractor Name: Colorado Engineering, Inc. Contractor Address: 1915 Jamboree Dr. Colorado Springs, CO 80920 Expiration of SBIR Data Rights: Expires 5 years after completion of project work for this or any follow-on SBIR contract, whichever is later. The Government's rights to use, modify, reproduce, release, perform, display, or disclose technical data or computer software marked with this legend are restricted during the period shown as provided in paragraph (b)(4) of the Rights in Noncommercial Technical Data and Computer Software—Small Business Innovative Research (SBIR) Program clause contained in the above identified contract. No restrictions apply after the expiration date shown above. Any reproduction of technical data, computer software, or portions thereof marked with this legend must also reproduce the markings.

ITAR Notice: Exports of information/data contained herein may be subject to the export laws of the United States including, but not limited to, the US International Traffic in Arms Regulations (ITAR), and may require advance authorization from the U.S.

ITAR Notice: Exports of information/data contained herein may be subject to the export laws of the United States including, but not limited to, the US International Traffic in Arms Regulations (ITAR), and may require advance authorization from the U.S. Government. The parties shall not export, disclose or transfer any such data directly or indirectly without compliance with this or any other applicable laws and regulations. This material provides up-to-date general information on product performance and use. It is not contractual in nature, nor does it provide warranty of any kind. Information is subject to change at any time. Copyright © Colorado Engineering, Inc. 2021. All Rights Reserved. All trademarks used herein are the property of their respective owners. Product Datasheet Revision 111103-1. www.coloradoengineering.com

# **SPECIFICATIONS**

| Memory—HMC                                                                                           | Health Monitoring                                                                                                                        | Power                                                                                                                                                                                                     |  |  |

|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <ul> <li>4/8 GB RAM</li> <li>70% less power than DDR3</li> <li>Up to 17X Faster than DDR3</li> </ul> | <ul> <li>Board voltages</li> <li>Temperature of K61, PCIe switch, FPGA</li> <li>Two external temperature sensors</li> <li>I2C</li> </ul> | <ul> <li>Power consumption: 12V @ 15.5 amps<br/>(subject to FPGA loading)</li> <li>Supply options: 12V power cable</li> <li>Additional power features: e-fuse/<br/>continuous power monitoring</li> </ul> |  |  |

# **CONFIGURATIONS**

| Model Number            | Configuration                                        |

|-------------------------|------------------------------------------------------|

| 3DR-A10-ADC-10GSPS -4-C | 4 Channel @ 2.5 GSPS each, commercial temp 0°C—50°C  |

| 3DR-A10-ADC-10GSPS -2-C | 2 Channel @ 5 GSPS each, commercial temp 0°C—50°C ** |

| 3DR-A10-ADC-10GSPS -1-C | 1 Channel @ 10 GSPS, commercial temp 0°C—50°C **     |

<sup>\*\*</sup> Check for availability — these configurations require interleaving board

<sup>\*</sup>Please contact CEI for extended temperature range options

|                  | Half Duplex (FPGA<br>LVDS@1.6GHz) |                       |                         | Full Duplex    |                | Bandwidth           |                            |                                   |                               |

|------------------|-----------------------------------|-----------------------|-------------------------|----------------|----------------|---------------------|----------------------------|-----------------------------------|-------------------------------|

| 3DR<br>Connector | # of Clusters                     | # of<br>LVDS<br>Pairs | LVDS<br>Total<br>(MB/s) | PCIe x4 (MB/s) | PCIe x4 (MB/s) | SerDes x4<br>(MB/s) | Bandwidth per<br>Connector | Total<br>Bandwidth<br>per X, Y, Z | Total<br>Bandwidth per Module |

| Y                | 2                                 | 7                     | 2,800                   | 8,000          | 8,000          | 8,000               | 26.2 GB/s                  | 52.3 GB/s                         |                               |

| Z2               | 1                                 | 7                     | 1,400                   | 8,000          | 8,000          | 8,000               | 24.8 GB/s                  | 24.8 GB/s                         | 133 GB/s                      |

| HS               | 1                                 | 6                     | 1,200                   | 8,000          | 8,000          | 48,000              | 55.9 GB/s                  | 55.9 GB/s                         |                               |

This material provides up-to-date general information on product performance and use. It is not contractual in nature, nor does it provide warranty of any kind. Information is subject to change at any time. Copyright © Colorado Engineering ITAR Notice: Exports of information/data contained herein may be subject to the export laws of the U.S. Government. The parties shall not export, disclose or transfer any such data directly or indirectly without compliance with this or any other applicable laws and regulations.