# **Crestone**

# Altera Stratix V FPGA Freescale T4240 Processor

Model Number: 3DR-S5-T4240

3DR computing technology brings together high performance computing, ease of programmability, low-cost, and commercial I/O flexibility in a modular, open systems and standards architecture to realize uniquely scalable and widely configurable, high speed embedded processing solutions for the development of radar, EW, SIGINT, and communication systems.

3DR Computing possesses the unique ability to morph in size, shape, and processing capacity. This flexibility provides a low cost, standard solution capable of rapidly conforming to the vastly different power, space, and environmental requirements found aboard any surface, sub-surface, or airborne system or platform.

#### **FEATURES**

## Altera Stratix V 5SGS-ED8N1F45I2N

- Free Scale T4240 (1.8 GHz)

- Freescale K61

- PLX PCIe 3D Mesh

- SerDes 3D Mesh

- LVDS 3D Mesh

- DDR3: 12GB DDR3@1600 MT/s (3 memory controllers with 4GB each)

- NAND flash: 512MB

- Operating System (OS): CEI Customized Linux

# **APPLICATIONS**

- General Purpose

- Digital Signal Processing

- Radar Receiver/Exciter

- Electronic Warfare/ Attack Systems

- Digital Array Processing & Beamforming

- SIGINT (ELINT, COMINT, etc.)

- Systems Digital Image Processing

Remote Sensing

## PRODUCT DESCRIPTION

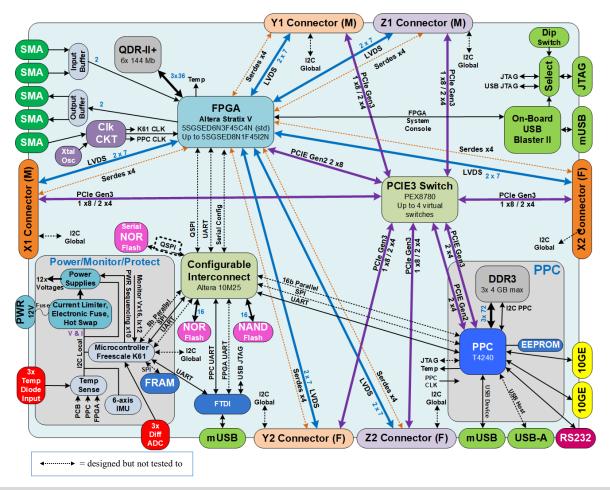

At the heart of the 3DR family architecture is the 3DR-S5-T4240 processor module, known as Crestone. This module consists of a power PC (Freescale T4240) general purpose and communications processor, an Altera Stratix V FPGA, on board DDR3 memory modules, and a combination of PCIe Gen 3, LVDS, and SERDES commercially available I/O modules. The processing modules also provide dual 10G Ethernet ports, JTAG, and UART-over-USB. The variety of available standard interfaces promotes network connectivity with a wide range of third party systems and subsystems. This includes commercially available switches and routers and promotes the integration of a system-of-systems in a net-centric environment.

The 3DR standard micro-controller architecture is interfaced through the I2C bus to provide FPGA and PPC temperature, voltage, current, and clock monitoring for automatic shut-down during critical over heat and/or voltage conditions. As with all 3DR modules, Crestone board supports 3D connectivity, allowing the user to stack and/or tile modules to address a wide variety of processing, I/O, size, weight, and power requirements.

### CONFIGURATIONS

| Model Number   | Configuration                      |  |

|----------------|------------------------------------|--|

| 3DR-S5-T4240-P | T4240 only, no StratixV            |  |

| 3DR-S5-T4240-C | Commercial Temp — 0°C - 50°C       |  |

| 3DR-S5-T4240-S | Trusted computing platform version |  |

| 3DR-Cables     | 6" high speed inter-module cables  |  |

\*Please contact CEI for extended temperature range options

SBIR DATA RIGHTS: Contract#: HQ0006-08-C-7908 Contract#: HQ0006-08-C-7908 Contractor Name: Colorado Engineering, Inc. Contractor Address: 1915 Jamboree Dr. Ste 165, Colorado Springs, CO 80920 Expiration of SBIR Data Rights: Expires 5 years after completion of project work for this or any follow-on SBIR contract, whichever is later. The Government's rights to use, modify, reproduce, release, perform, display, or disclose technical data or computer software marked with this legend are restricted during the period shown as provided in paragraph (b)(4) of the Rights in Noncommercial Technical Data and Computer Software—Small Business Innovative Research (SBIR) Program clause contained in the above identified contract. No restrictions apply after the expiration date shown

provided in paragraph (b)(4) of the Rights in Noncommercial Technical Data and Computer Software-Small Business Innovative Research (SBIR) Program clause contained in the above identified contract. No restrictions apply after the expiration date shown above. Any reproduction of technical data, computer software, or portions thereof marked with this legend must also reproduce the markings.

ITAR Notice: Exports of information/data contained herein may be subject to the export laws of the United States including, but not limited to, the US International Traffic in Arms Regulations (ITAR), and may require advance authorization from the U.S. Government. The parties shall not export, disclose or transfer any such data directly or indirectly without compliance with this or any other applicable laws and regulations. This material provides up-to-date general information on product performance and use. It is not contractual in nature, nor does it provide warranty of any kind. Information is subject to change at any time. Copyright © Colorado Engineering, Inc. 2021. All Rights Reserved. All trademarks used herein are the property of their respective owners. Product Datasheet Revision 111103-1. www.coloradoengineering.com

#### PRODUCT SPECIFICATIONS

| Altera Stratix V FPGA      | 864 Mb QDR-II+                | LVDS 3D Mesh  | 2 clusters of 7 LVDS per connector                            |

|----------------------------|-------------------------------|---------------|---------------------------------------------------------------|

|                            | LVDS                          |               | 14 Gbps in X. Y, Z                                            |

|                            | SerDes                        | FreeScale K61 | Controls power sequencing                                     |

|                            | PCIe Gen2                     |               | Monitors temperatures, voltages, and currents                 |

|                            | JTAG Programmable             | PCIe 3D Mesh  | 1x8 or 2x4 per connector                                      |

|                            | Master BPI Configuration      | Power         | Power consumption: 12V @ 6Amps (subject to FPGA loading)      |

|                            | Write Protect Available       |               | Supply options: 12V power cable                               |

|                            | QDR-II+: 864Mb at 450 MT/s    |               | Additional power features: e-fuse/continuous power monitoring |

| FreeScale T4240            | 12 cores/24 virtual cores     | Physical      | Board dimensions: 6.25" L x 6.25" W                           |

|                            | 2 - 10 GbE Ports              |               | Board dimensions with connectors: 6.668" L x 6.668" W         |

|                            | PCIe Gen3                     |               | Distance between boards (stacked, board-to-board): 0.990"     |

| <b>External Interfaces</b> | Two 10G Ethernet ports        |               | Weight: 12.2 oz                                               |

|                            | PCIe Gen3                     | Environmental | Operating temperature: 0°C to +50°C                           |

|                            | All X, Y, Z connectors        |               | Storage temperature: (est) -40°C to +105°C                    |

|                            | FPGA: SERDES, LVDS, PCIE      |               | Cooling requirements: application specific                    |

|                            | PPC: PCIE                     |               |                                                               |

|                            | RS-232: PPC                   |               |                                                               |

|                            | UART-over-USB: PPC, FPGA, K61 |               |                                                               |

|                            | Microcontroller, FPGA         |               |                                                               |